Análisis de tiempo en el diseño de PCB de alta velocidad

Mar 04, 2022

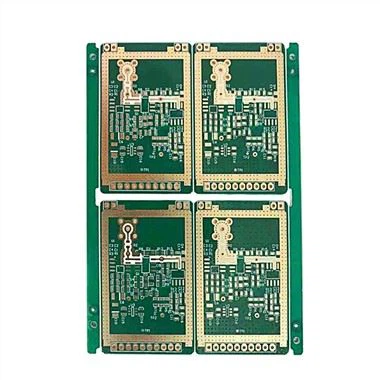

Para los ingenieros de diseño de sistemas digitales, el análisis de tiempo es una parte importante del diseño de PCB de alta-velocidad. Especialmente con el surgimiento del bus 100M, después de que la tasa de flanco de la señal alcanza los picosegundos, el rendimiento del sistema depende más del diseño del front-end, lo que requiere un análisis y cálculo de tiempo preciso al comienzo del diseño. El análisis de tiempo y la integridad de la señal son inseparables, y la buena calidad de la señal es la clave para garantizar las relaciones de tiempo. Es probable que los problemas de calidad de la señal causados por la reflexión, la diafonía y otros fenómenos generen cambios de tiempo y desorden, y debemos considerar los dos juntos al diseñar.

El punto de partida del análisis de temporización es determinar el esquema de diseño de acuerdo con el establecimiento de la señal o la relación de tiempo de espera. Este método se ejecuta a través de todo el proceso de diseño, incluido el diseño de circuitos integrados, el diseño de placas y el diseño de sistemas.

El tiempo-de-vuelo se refiere a la diferencia desde el momento en que se envía la señal hasta el momento en que la señal es estable en el extremo receptor, y se utiliza para expresar el retraso causado por el cableado y la carga. . En el caso de baja velocidad, se puede determinar mediante un método aproximado, pero en el diseño de pcb de alta-velocidad, debe determinarse mediante un método de simulación debido a factores como la carga y el efecto de la línea de transmisión. Una vez que se determina el tiempo de vuelo, el cálculo del tiempo se puede implementar utilizando una tabla o un método manual para verificar si la señal cumple con los requisitos de muestreo y retención de la señal. De manera similar, invierta este proceso para obtener reglas de longitud de enrutamiento.

La característica del modo de reloj común es que los relojes de los transceptores son proporcionados por la fuente de reloj común. Tiene dos características. Una es que los datos deben llegar al extremo receptor dentro de un ciclo y la segunda es que la diferencia de reloj tiene una gran influencia en el tiempo.

Por lo general, cuando el reloj y los datos son controlados por el mismo tipo de interfaz, el cálculo de tiempo solo necesita considerar la diferencia de fase entre ellos. Si este no es el caso, la diferencia de fase (como la longitud del cableado) debe ajustarse de acuerdo con el tiempo de vuelo. El método en el sentido de que el enrutamiento del reloj de datos tiene la misma longitud se vuelve ineficaz.

En el diseño, otros factores como el ruido de conmutación, la interferencia entre -símbolos y los bucles no-ideales tienen un impacto en la fase de la señal. Por lo tanto, por un lado, debemos agregar razonablemente márgenes de diseño en el diseño de tiempo y, por otro lado, debemos adoptar otros métodos de diseño para reducir la influencia de la interferencia.